AI desenvolve modelo inovador para linguagem de design de chips

São Paulo — InkDesign News —

Pesquisadores da NYU Tandon School of Engineering desenvolveram um modelo de inteligência artificial (IA) especializado, denominado VeriGen, para a geração de código em Verilog, uma linguagem de programação que descreve o funcionamento da circuitaria de chips.

Contexto da pesquisa

A pesquisa recente recebeu o prêmio de Melhor Artigo do ACM Transactions on Design Automation of Electronic Systems 2024, destacando-se como um avanço significativo na automação da criação de linguagens de descrição de hardware, que tradicionalmente exigiam expertise técnica profunda. “Modelos de IA de propósito geral não são muito bons em gerar código Verilog, porque há pouca disponibilidade de código Verilog na Internet para treinamento,” afirmou o autor principal, o Professor do Instituto Siddharth Garg, da NYU Tandon. (“General purpose AI models are not very good at generating Verilog code, because there’s very little Verilog code on the Internet available for training.”)

— Siddharth Garg, Professor, NYU Tandon School of Engineering

Método proposto

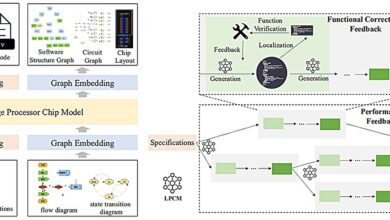

Para enfrentar esse desafio, a equipe de Garg criou e distribuiu o maior conjunto de dados de treinamento de código Verilog já montado, coletando cerca de 50.000 arquivos de Verilog de repositórios públicos do GitHub e complementando com conteúdo de 70 livros didáticos de Verilog. O modelo mais robusto foi desenvolvido a partir do ajuste fino do modelo CodeGen-16B, de fontes abertas da Salesforce, que contém 16 bilhões de parâmetros e foi originalmente pré-treinado em código de linguagem natural e de programação.

O processo de treinamento exigiu três GPUs NVIDIA A100 operando em paralelo, com os parâmetros do modelo consumindo 30 GB de memória e o treinamento completo requerendo aproximadamente 250 GB de memória de GPU.

Resultados e impacto

O modelo ajustado apresentou desempenho superior em testes, superando modelos comerciais de ponta, sendo uma ordem de magnitude menor e completamente de código aberto. O CodeGen-16B ajustado obteve uma taxa de 41,9% de código funcionalmente correto, contra 35,4% do modelo comercial code-davinci-002, com a precisão aumentando de apenas 1,09% para 27% após o ajuste. Isso demonstra a significativa vantagem do treinamento específico de domínio.

“Mostramos que ajustando um modelo para uma tarefa específica, você pode obter reduções de magnitude na dimensão do modelo,” destacou Garg, sublinhando como sua abordagem melhorou tanto a precisão quanto a eficiência.

— Siddharth Garg, Professor, NYU Tandon School of Engineering

Com o intuito de democratizar o design de hardware, VeriGen já gerou interesse significativo na indústria. Modelos avançados chamados “CL Verilog” foram desenvolvidos e fornecidos a empresas de hardware, como Qualcomm e NXP, para avaliação de potenciais aplicações comerciais. A pesquisa se constrói sobre esforços anteriores da NYU Tandon, incluindo o projeto DAVE de 2020, que visava derivar automaticamente Verilog do inglês.

Essas inovações podem servir como base para futuras iniciativas em design de chips e sistemas de IA. Fontes indicam que novos passos na pesquisa podem fomentar ainda mais avanços significativos no campo, especialmente na utilização de IA para automação em design de hardware.

Fonte: (TechXplore – Machine Learning & AI)