Nova Arquitetura de Chip Reduz Uso de Energia em AI

Pesquisadores de Cornell desenvolveram uma nova arquitetura de chip que reduz significativamente o consumo de energia em sistemas de inteligência artificial (AI), um passo importante para mitigar as pegadas de carbono de data centers.

Contexto da pesquisa

Com o aumento da demanda por poder computacional em machine learning, surge a necessidade urgente de soluções mais sustentáveis. A equipe, composta por especialistas de Cornell Tech e Cornell Engineering, está explorando novos caminhos para tornar a hardware de AI mais eficiente e menos dependente de energia.

Método proposto

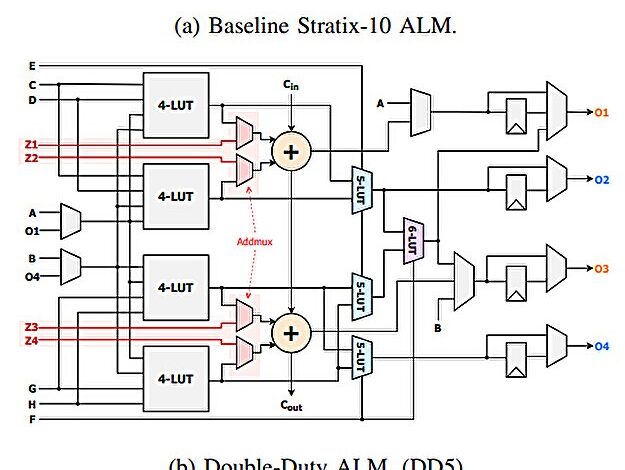

Os pesquisadores focaram em FPGAs (Field-Programmable Gate Arrays), chips altamente flexíveis que podem ser reprogramados após a fabricação. “FPGAs estão em toda parte—de placas de rede a máquinas de ultrassom,” disse o coautor Mohamed Abdelfattah, professor assistente em Cornell Tech. “AI está chegando a todos esses dispositivos, e esta arquitetura ajuda a tornar essa transição mais eficiente” (

“AI está chegando a todos esses dispositivos, e esta arquitetura ajuda a tornar essa transição mais eficiente”

(“AI is coming to all of these devices, and this architecture helps make that transition more efficient.”)— Mohamed Abdelfattah, Professor Assistente, Cornell Tech

). O novo design, denominado “Double Duty,” permite que as Lookup Tables (LUTs) e as cadeias de adição operem de forma independente dentro do mesmo bloco lógico, aumentando a eficiência dos chips durante tarefas que exigem operações aritméticas complexas, como reconhecimento de imagem.

Resultados e impacto

Os testes mostraram que a nova arquitetura reduziu o espaço necessário para tarefas específicas de AI em mais de 20% e melhorou o desempenho geral em quase 10%. Esses resultados indicam que é possível utilizar menos chips para realizar o mesmo trabalho, diminuindo assim o uso de energia. “Essa mudança também beneficia indústrias tradicionais,” afirmou Xilai Dai, coautor do estudo. “Você pode encaixar programas maiores em chips menores, o que melhora a eficiência em geral” (

“Você pode encaixar programas maiores em chips menores, o que melhora a eficiência em geral”

(“You can fit larger programs into smaller chips, which improves efficiency across the board.”)— Xilai Dai, Estudante de Doutorado, Cornell Engineering

).

A pesquisa iniciou como um projeto de graduação e evoluiu para um estudo mais abrangente, envolvendo colaborações com universidades canadenses e engenheiros da Altera. O avanço na arquitetura “Double Duty” representa um passo crucial no uso eficiente de FPGAs, tornando-os dispositivos computacionais realmente eficazes, com grandes implicações para a indústria de AI e outras áreas que requerem operações aritméticas intensivas.

Em termos de aplicações, essa nova abordagem pode ser adaptada para chips em dispositivos médicos, comunicações sem fio e até em veículos autônomos, expandindo ainda mais as fronteiras da AI.

Fonte: (TechXplore – Machine Learning & AI)